# Quantization – 1 EECE695D: Efficient ML Systems

Spring 2025

### Agenda

- Question. How do we reduce the computational cost of matmuls?

- W2. Sparsity

- i.e., reducing the number of nonzero elements

- W3. Quantization

- i.e., reducing the precision of weights

<u>Note</u>. Many graphics from Song Han's lecture notes

Basic idea

### Quantization

- Approximating some  $X \in \mathcal{X}$  by an element of small, discrete subset  $\mathcal{Y} \subseteq \mathcal{X}$

- $\mathscr{X}$  may be either discrete (e.g., FP32) or continuous (e.g.,  $\mathbb{R}$ )

- Example. Approximating a float by an integer (e.g.,  $3.141592 \Rightarrow 3$ )

# Weight Quantization

• We quantize the weights of a matrix, so that

$$\begin{bmatrix} 2.43 & 1.72 \\ 9.72 & -3.28 \end{bmatrix} \begin{bmatrix} x_1 & x_2 \\ x_3 & x_4 \end{bmatrix}$$

- Memory. Less bits to store and transfer

- <u>Computation</u>. Less operations to be done

(as we'll see, it depends on how we quantize)

$$\Rightarrow \begin{bmatrix} 2 & 2 \\ 10 & -3 \end{bmatrix} \begin{bmatrix} x_1 & x_2 \\ x_3 & x_4 \end{bmatrix}$$

### **Activation Quantization**

• Plus, we will often do activation quantization (i.e., x)

$$\begin{bmatrix} 2.43 & 1.72 \\ 9.72 & -3.28 \end{bmatrix} \begin{bmatrix} -1.12 & 2.21 \\ 5.27 & 2.09 \end{bmatrix}$$

- Example. If weights and input are integers:

- Outputs are integers

- After ReLU, will remain as an integer

$\Rightarrow$  All ops are integers!

# $\begin{vmatrix} 2 \\ 9 \end{vmatrix} \qquad \Rightarrow \qquad \begin{vmatrix} 2 & 2 \\ 10 & -3 \end{vmatrix} \begin{vmatrix} -1 & 2 \\ 5 & 2 \end{vmatrix}$

# Problem formulation

### **Problem formulation**

- Minimize the training loss of a model with quantized parameters

- minimize

- Here,  $q(\cdot)$  is a quantization function

- Applied entrywise (scalar quant.) or blockwise (vector quant.)

- We assume scalar quantization

- Different  $q(\cdot)$  is used for each tensor

$$\hat{L}_{\mathbf{W},q(\cdot)} \quad \hat{L}(q(\mathbf{W}))$$

### **Problem formulation**

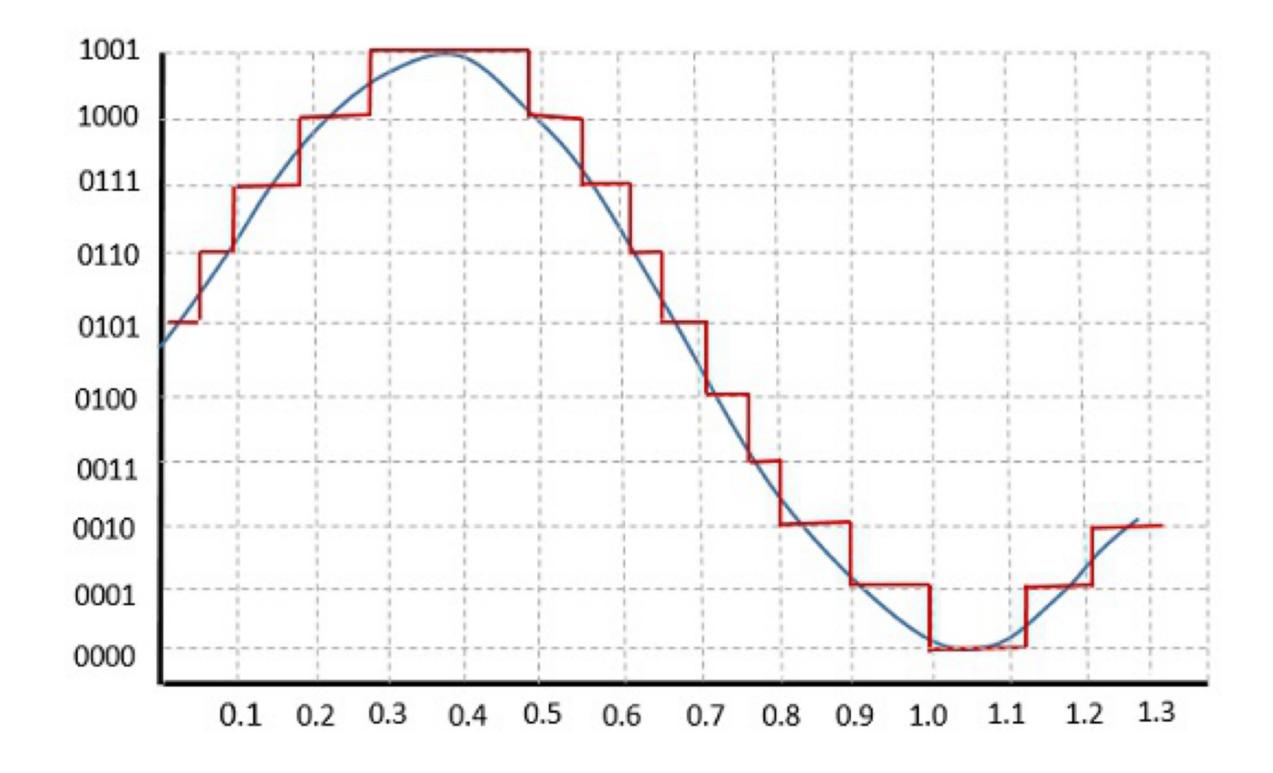

• The (scalar) quantization function  $q(\cdot)$  consists of two functions:

- Partitions the space into K groups

- - Decides an output for each partition

- $q = g \circ f$

- Encoder  $f: \mathbb{R} \to \{1, \dots, K\}$  generates codes from inputs

- **Decoder**  $g : \{1, \dots, K\} \to \mathbb{R}$  approximates inputs from codes

### (using $\log_2 K$ bits per entry)

# Algorithm

## Algorithms

- Typically solved by:

- (full-precision) • Train **W**

- Optimize  $q(\cdot)$

- Further tune w (low-precision)

Another option: Do quantized training from scratch (later)

minimize<sub>**w**,q(·)</sub>  $\hat{L}(q(\mathbf{w}))$

## Optimizing $q(\cdot)$

- Difficult to optimize using  $\hat{L}(\cdot)$

- **Popular.** Relax it to a weight approximation:

- Here, dist( $\cdot, \cdot$ ) is some distance measure (e.g.,  $\ell^2$  distance)

- This is equivalent to:

$\min_{C=\{c_1,\ldots,c_k\}} \min_{\tilde{W}_1,\ldots,\tilde{W}_d \in C} \operatorname{dist}(\tilde{\mathbf{w}}, \mathbf{w})$

• C is the "codebook"

minimize<sub>w,q(·)</sub> dist(q(w), w)

### Key issue

$$\min_{C=\{c_1,\ldots,c_k\}}$$

- A key issue here is to choose the search space of C wisely.

- Storage-oriented. No constraint

- e.g., K-means quantization

- Computation-oriented. Use HW-friendly data types (e.g., INT)

- e.g., linear quantization

- we'll review data types very soon

min  $dist(\tilde{w}, w)$  $\tilde{w}_1,\ldots,\tilde{w}_d \in C$

### Another issue

$\min_{C=\{c_1,\ldots,c_k\}}$

- Of course, this relaxation is not as good as directly minimizing  $\hat{L}(\;\cdot\;)$

- Thus we perform further tuning

- Advanced calibration

- Quantization-aware training (QAT)

- (...)

$$\min_{\tilde{w}_1,\ldots,\tilde{w}_d \in C} \operatorname{dist}(\tilde{w}, w)$$

- Today

- Recap on data types

- K-means quantization

- Next class

- Linear quantization

- Additional tricks

### Agenda

# Recap: Data type numerics

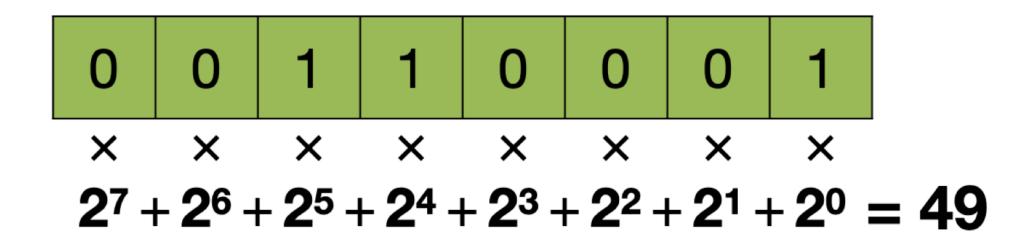

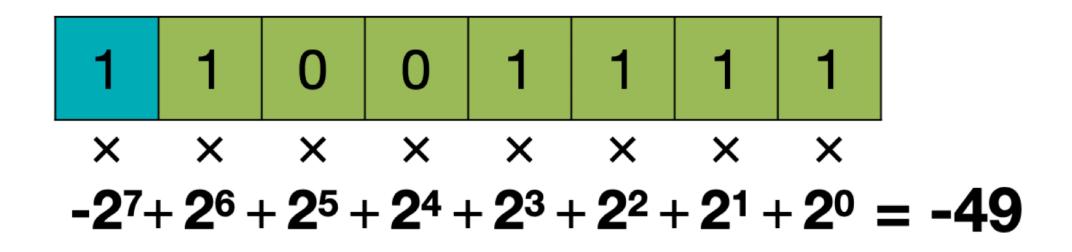

• Given *n* bits, the value will be computed as

• Covers the range  $\{0, ..., 2^n - 1\}$

Integer (unsigned)

$\sum_{i=1}^{n} b_i \cdot 2^{n-i}$

i=1

- Same as unsigned integer, but uses the first bit to represent sign

- O: Positive

- 1: Negative

- Two conventions:

- Sign-magnitude

- Two's complement

Integer (signed)

| 1 | 0 | 0 | 0 | 1 |

|---|---|---|---|---|

|---|---|---|---|---|

- Multiplicative representation of sign

- First bit represents  $\times (-1)$

- 000...00 denotes zero

- 100...00 also denotes zero

- Covers the range  $\{-2^{n-1}-1, \dots, 2^{n-1}-1\}$

### **INT: Sign-magnitude**

$(-1)^{\text{sign}} \times (\text{uint}_{n-1})$

### (negative zero; one symbol wasted)

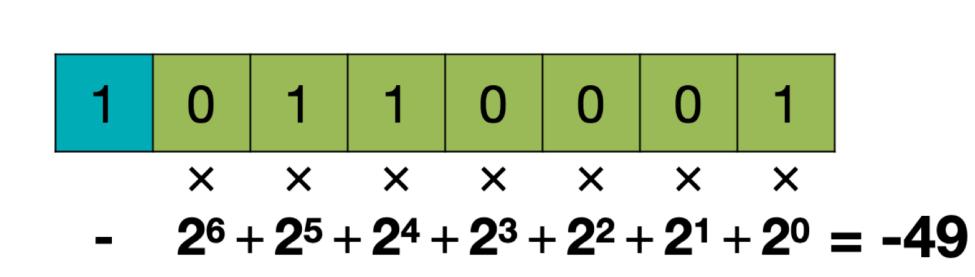

- Additive representation of sign

- Uses the first bit to represent  $-2^{n-1}$

- 000...00 denotes 0

- 100...00 denotes  $-2^{n-1}$

- Covers the range  $\{-2^{n-1}, \dots, 2^{n-1}-1\}$

### INT: Two's complement

$(\text{sign bit}) \cdot (-2^{-n}) + (\text{uint}_{n-1})$

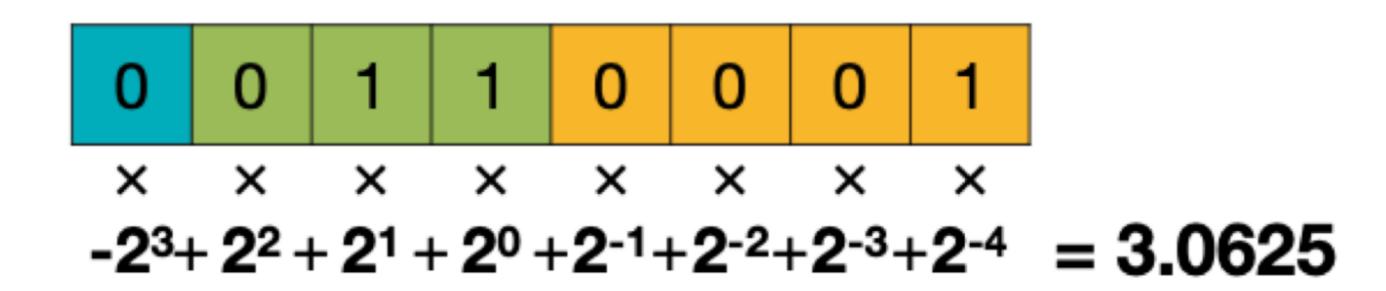

### Fixed-point numbers

• Shifts INT by a fixed decimal point

$$(-1)^{sign}$$

×

- Used for low-cost microprocessors

- For early uses in DL, see <u>Vanhouke'11</u>, <u>Hwang&Sung'14</u>

$(uint_{n-1}) \times 2^{-d}$

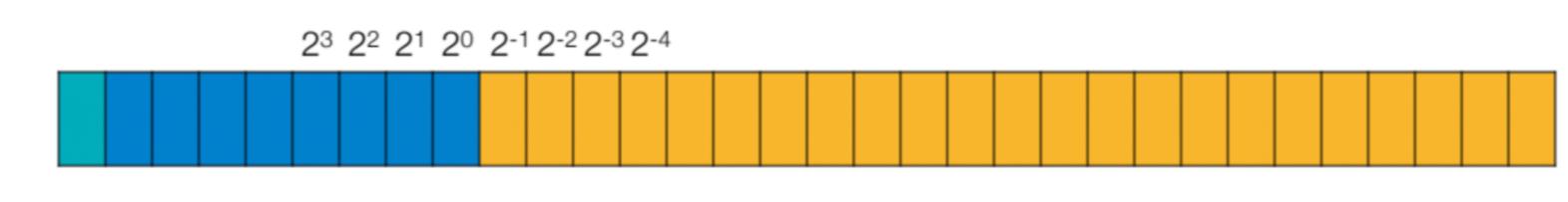

# Floating-point numbers

- IEEE 754 standard

- Decimal point is flexibly represented with exponent bits

$$(-1)^{\text{sign}} \times (1 + \text{Fr})$$

• There exists an exponent bias of -127

• **Question.** How do we represent zero?

### Sign 8 bit Exponent

raction)  $\times$  2<sup>(Exponent)-127</sup>

### 23 bit Fraction

# Floating-point numbers

- <u>Answer.</u> We allocate special symbols to represent end cases

- If exponent bits are OO...O, we apply a special rule  $(-1)^{\text{sign}} \times (\text{Fraction}) \times 2^{1-127}$

- By letting fraction bits be OO...O, we get zero

- If exponent bias are 11...1, we apply the rules:

- if fraction bits are OO...O, denotes  $\infty$

- else, denotes NaN

(wasted bits!)

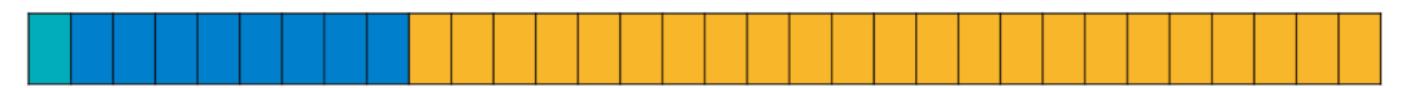

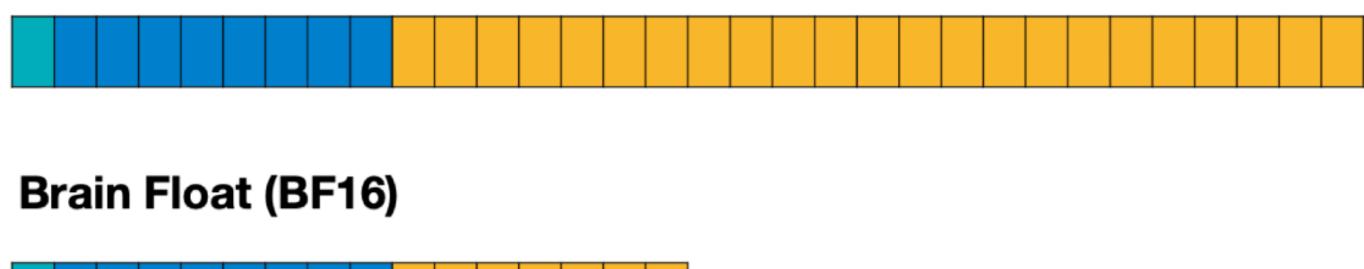

- FP16 uses less dynamic range and less precision than FP32

- Exponent: 8 -> 5

- Fraction: 23 —> 10

**IEEE Half Precision 16-bit Float (IEEE FP16)**

### **FP16**

- Introduced by Google Brain (thus called brain float)

- BF16 uses the same dynamic range and less precision than FP32

- Exponent: 8 -> 8

- Fraction: 23 —> 7

### **BF16**

- Introduced in NVIDIA Ampere architectures; stands for "tensor float"

- Uses 19 bits

- Exponent: 8

- Fraction: 23 -> 10

**Brain Float (BF16)**

**Nvidia TensorFloat (TF32)**

(same as BF16)

(same as FP16)

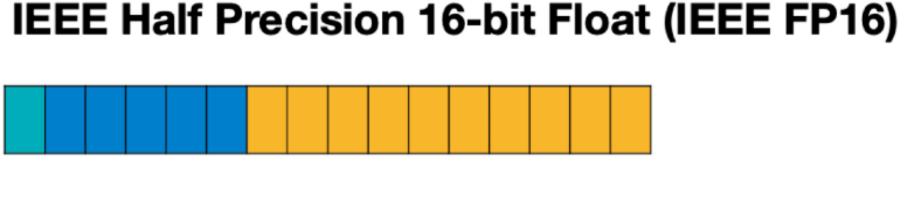

- Multiple standards

- Different companies

- Inference (precision) / Backward (range)

- Example. NVIDIA FP8 (in H100)

### Nvidia FP8 (E4M3)

### **Nvidia** FP8 (E5M2) for gradient in the backward

$\mathbf{FP8}$

\* FP8 E4M3 does not have INF, and S.1111.111<sub>2</sub> is used for NaN. \* Largest FP8 E4M3 normal value is S.1111.1102 = 448.

\* FP8 E5M2 have INF (S.11111.00<sub>2</sub>) and NaN (S.11111.XX<sub>2</sub>). \* Largest FP8 E5M2 normal value is S.11110.112 = 57344.

### Very limited dynamic range

FP4

### • Yet, the possibility is open

• Blackwell has added support for FP6, FP4

|                                                | Blackwell                                   | Hopper                            |  |

|------------------------------------------------|---------------------------------------------|-----------------------------------|--|

| Supported Tensor Core<br>precisions            | FP64, TF32, BF16, FP16, FP8, INT8, FP6, FP4 | FP64, TF32, BF16, FP16, FP8, INT8 |  |

| Supported CUDA <sup>®</sup> Core<br>precisions | FP64, FP32, FP16, BF16                      | FP64, FP32, FP16, BF16, INT8      |  |

| Ampere |

|--------|

|--------|

| Ampere                                          | Turing                    | Volta                     |

|-------------------------------------------------|---------------------------|---------------------------|

| FP64, TF32, bfloat16,<br>FP16, INT8, INT4, INT1 | FP16, INT8, INT4, INT1    | FP16                      |

| FP64, FP32, FP16,<br>bfloat16, INT8             | FP64, FP32, FP16,<br>INT8 | FP64, FP32, FP16,<br>INT8 |

### FP4

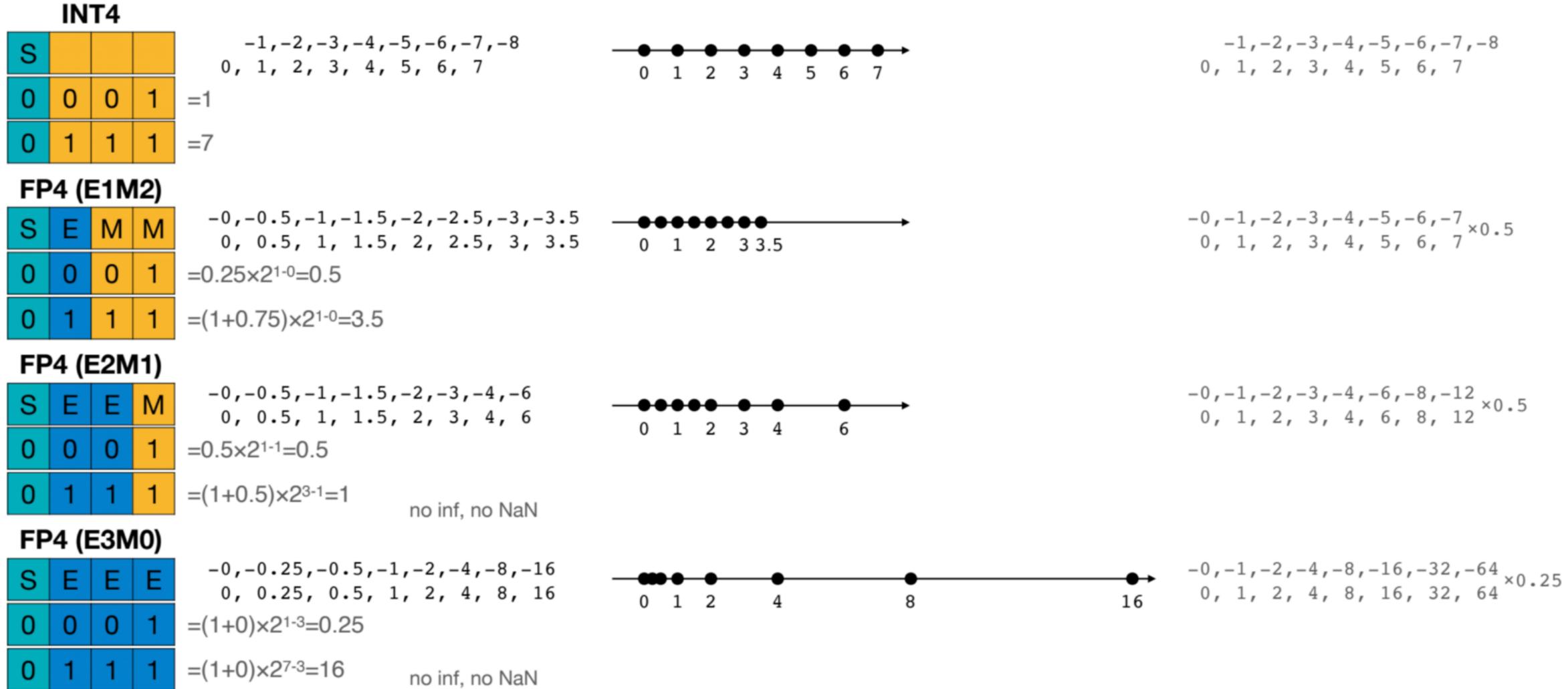

### Numerics vs. Throughput

• On A100 GPU math, the relative throughput are:

### FP16/BF16

### 16x

Table 1. Relative throughput of A 100 GPU math.

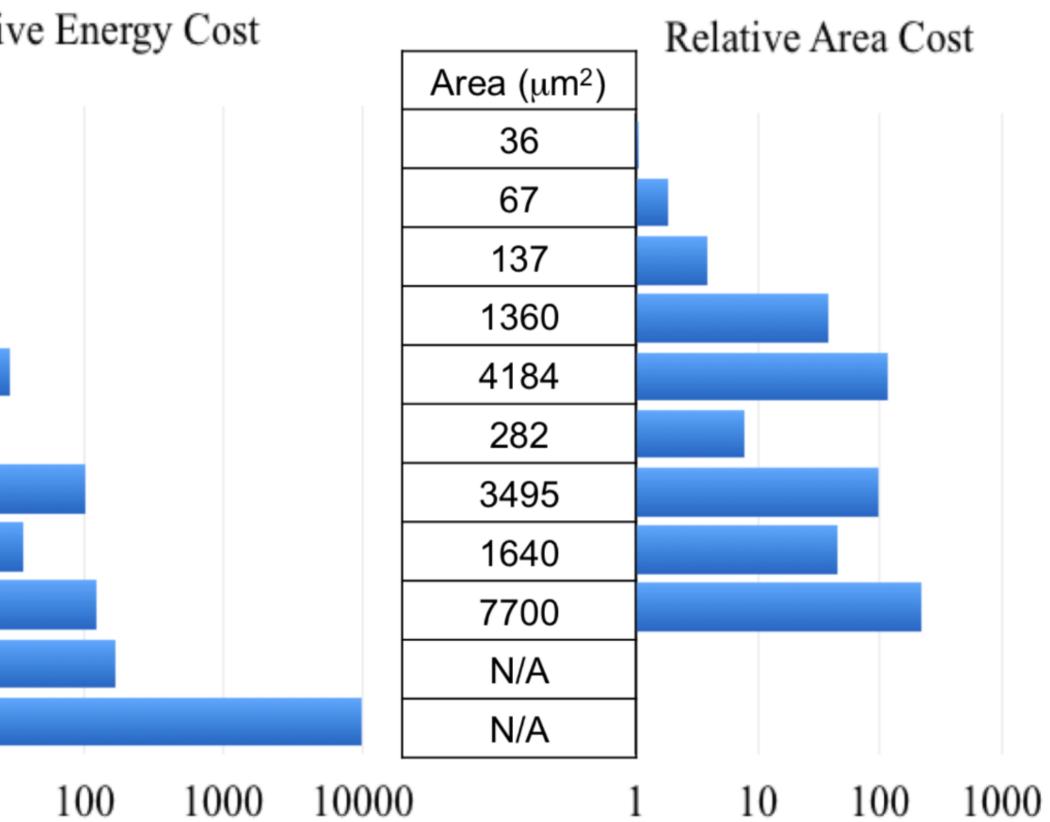

# Numerics vs. Energy & Chip area

On TSMC 45nm 0.9V, different data types and bitwidths translate into:

|                     |             | Relativ |

|---------------------|-------------|---------|

| Operation:          | Energy (pJ) |         |

| 8b Add              | 0.03        |         |

| 16b Add             | 0.05        |         |

| 32b Add             | 0.1         |         |

| 16b FP Add          | 0.4         |         |

| 32b FP Add          | 0.9         |         |

| 8b Mult             | 0.2         |         |

| 32b Mult            | 3.1         |         |

| 16b FP Mult         | 1.1         |         |

| 32b FP Mult         | 3.7         |         |

| 32b SRAM Read (8KB) | 5           |         |

| 32b DRAM Read       | 640         |         |

|                     |             | . 10    |

Energy numbers are from Mark Horowitz "Computing's Energy Problem (and what we can do about it)", ISSCC 2014 Area numbers are from synthesized result using Design Compiler under TSMC 45nm tech node. FP units used DesignWare Library.

10

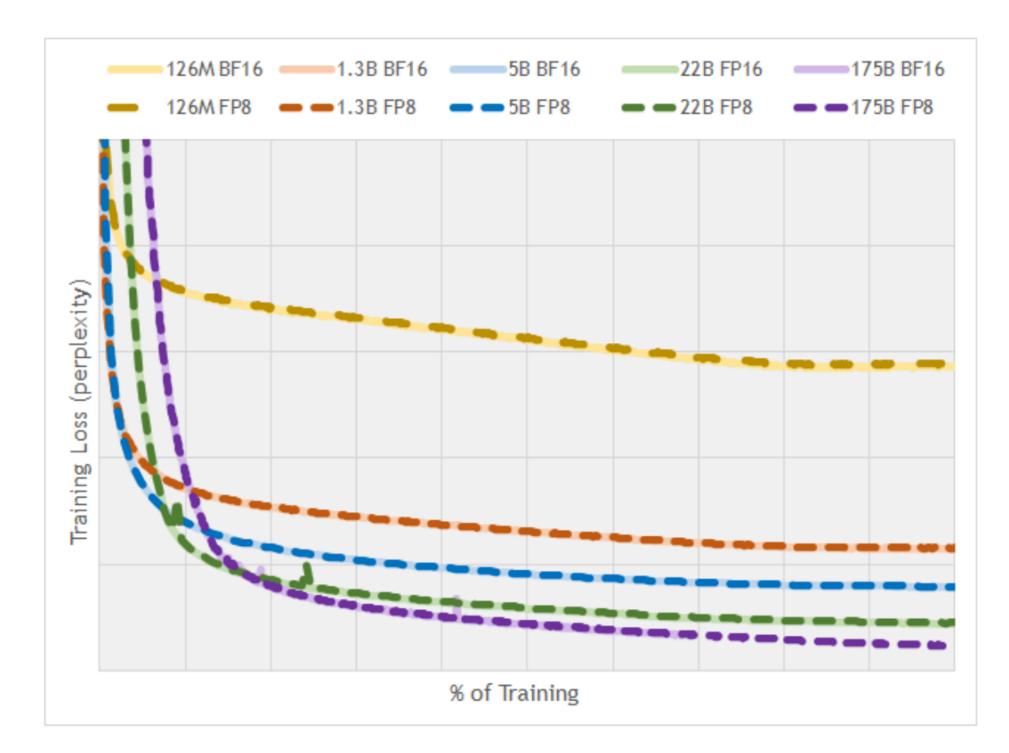

## Numerics vs. Training cost

- For certain cases, low-precision training is as good as high-precision

- Not always true, sadly

Figure 1: Training loss (perplexity) curves for various GPT-3 models. x-axis is normalized number of iterations.

**K-Means Quantization**

Recall that we were solving

- K-means quantization puts no constraint on C:

- **Storage.** Well optimized

- **Computation.** Cannot use low-bit matmuls  $\bullet$

### **K-Means Quantization**

# $\min_{C=\{c_1,\ldots,c_k\}} \min_{\tilde{W}_1,\ldots,\tilde{W}_d\in C} \operatorname{dist}(\tilde{\mathbf{w}},\mathbf{w})$

### Plus, requires weights to be decoded to full-precision before use

Han et al., "Deep Compression: Compressing DNNs with pruning, trained quantization, and Huffman coding," ICLR 2016

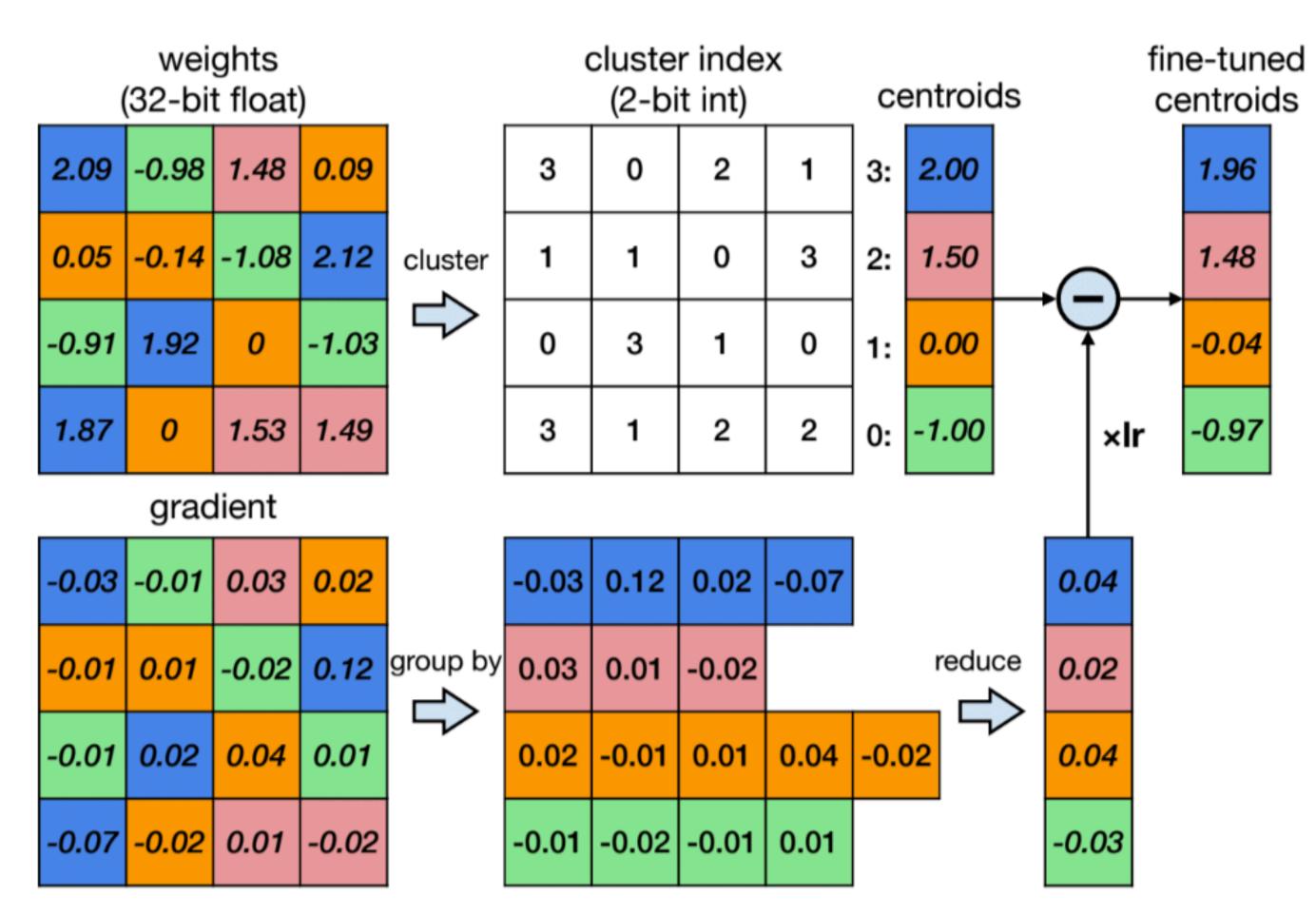

# Algorithm

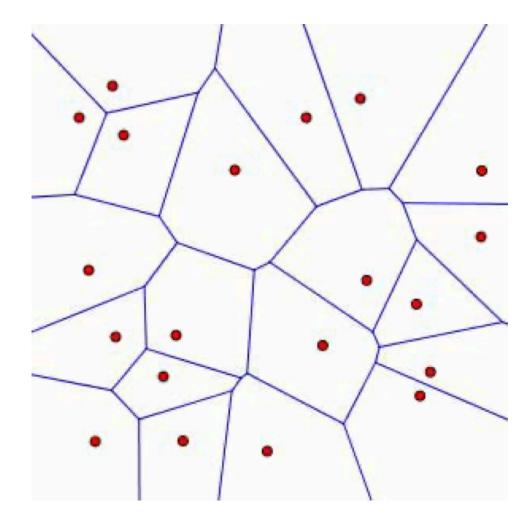

• K-means quantization simply use  $\ell^2$  distance:

$$\min_{C = \{c_1, \dots, c_k\}} \min_{\tilde{w}_1, \dots, \tilde{w}_d \in C} \sum_{i=1}^d (\tilde{\mathbf{w}}_i - \mathbf{w}_i)^2$$

- This is exactly 1D K-means, with neural network weights as the data.

- Solved via Lloyd's algorithm

- Assign weights to clusters by nearest neighbor matching

- Compute centroids via averaging

- Repeat until convergence

Han et al., "Deep Compression: Compressing DNNs with pruning, trained quantization, and Huffman coding," ICLR 2016

of the weights assigned to each cluster

## Algorithm

# • As $\ell^2$ loss is imperfect, we fine-tune the centroids using the average gradients

Han et al., "Deep Compression: Compressing DNNs with pruning, trained quantization, and Huffman coding," ICLR 2016

### Storage

- **Note.** We need to store the codebook as well!

$(\log_2 K)N^2/8 + 4K$

| weights<br>(32-bit float) |       |       |       |     |  |

|---------------------------|-------|-------|-------|-----|--|

| 2.09                      | -0.98 | 1.48  | 0.09  |     |  |

| 0.05                      | -0.14 | -1.08 | 2.12  | clı |  |

| -0.91                     | 1.92  | 0     | -1.03 |     |  |

| 1.87                      | 0     | 1.53  | 1.49  |     |  |

32 bit × 16 = 512 bit = 64 B

storage

• If we quantize  $N \times N$  matrix with codebook size K, the compression rate is

$4N^2$ cluster index centroids (2-bit int) 3 3: 2.00 0 2 1 1.50 3 2: 1 luster 0  $\Rightarrow$ 1: 0.00 0 3 0 0: -1.00 2 2 3 1 codebook indexes 32 bit  $\times$  4 2 bit × 16  $= 32 \text{ bit} \times 16 + 32 \text{ bit} \times 4 = 128 \text{ bit} = 16 \text{ B}$ **=** 20 B

3.2 × smaller

### Next Class

- Linear quantization

- Various issues

- Granularity

- Rescaling

- Clipping

- Rounding

- QAT